# IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re PATENT APPLICATION of

Kazuhide ABE :

Serial No.: [NEW] : Mail Stop Patent Application

Filed: January 29, 2004 : Attorney Docket No. OKI.612

For: WIRING STRUCTURE OF SEMICONDUCTOR DEVICE AND METHOD

OF MANUFACTURING THE SAME

## **CLAIM OF PRIORITY**

U.S. Patent and Trademark Office 2011 South Clark Place Customer Window, Mail Stop Patent Application Crystal Plaza Two, Lobby, Room 1B03 Arlington, VA 22202

Sir:

Applicant, in the above-identified application, hereby claims the priority date under the International Convention of the following Japanese application:

Appln. No. 2003-367951 filed October 28, 2003

as acknowledged in the Declaration of the subject application.

A certified copy of said application is being submitted herewith.

Respectfully submitted,

VOLENTINE FRANCOS, PLLC

Adam C. Volentine Registration No. 33,289

12200 Sunrise Valley Drive, Suite 150 Reston, Virginia 20191 Tel. (703) 715-0870

Fax. (703) 715-0877

Date: January 29, 2004

# 日本国特許庁 JAPAN PATENT OFFICE

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office.

出願年月日 Date of Application:

2003年10月28日

出 願 番 号 Application Number:

特願2003-367951

[ST. 10/C]:

[JP2003-367951]

出 願 人

Applicant(s):

沖電気工業株式会社

特許庁長官 Commissioner, Japan Patent Office 2003年12月24日

【書類名】 特許願 【整理番号】 GI000015

【提出日】平成15年10月28日【あて先】特許庁長官 殿【国際特許分類】H01L 23/522

【発明者】

【住所又は居所】 東京都港区虎ノ門1丁目7番12号 沖電気工業株式会社内

【氏名】 阿部 一英

【特許出願人】

【識別番号】 000000295

【氏名又は名称】 沖電気工業株式会社

【代表者】 篠塚 勝正

【代理人】

【識別番号】 110000165

【氏名又は名称】 グローバル・アイピー東京特許業務法人

【代表者】 宮川 良夫

【手数料の表示】

【予納台帳番号】 193162 【納付金額】 21,000円

【提出物件の目録】

【物件名】 特許請求の範囲 1

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

### 【書類名】特許請求の範囲

## 【請求項1】

複数の溝部が形成されており、隣接する溝部の間に水平方向の界面を有する第1絶縁膜と、

前記第1絶縁膜の溝部ごとに前記界面よりも突出して形成された複数の配線膜と、

前記配線膜の底面に形成されるとともに、前記配線膜の側面において前記界面より上方まで形成されている複数のバリア膜と、

少なくとも前記配線膜の上面に形成されており、溝部ごとに分離されている複数のキャップ膜と、を備えることを特徴とする半導体装置の配線構造。

### 【請求項2】

前記キャップ膜は、前記界面よりも突出した部分において、前記配線膜の上面から前記第1絶縁膜の界面に渡って形成されており、前記界面上で分離されていることを特徴とする、請求項2に記載の半導体装置の配線構造。

### 【請求項3】

前記キャップ膜は、前記配線膜及び前記バリア膜の上面のみに形成されていることを特徴とする、請求項2に記載の半導体装置の配線構造。

#### 【請求項4】

前記キャップ膜は、 $Si_x N_y$ 、 $Si_x C_y$ 、 $Si_x O_y N_z$ 又は $Si_x C_y$ を主成分とする絶縁膜であることを特徴とする、請求項2に記載の半導体装置の配線構造。

### 【請求項5】

前記キャップ膜は、TaxNy、Ta又は<math>TaxSiyNzからなる金属膜であることを特徴とする、請求項 2 に記載の半導体装置の配線構造。

## 【請求項6】

前記キャップ膜は、 $Ti_xN_y$ 又は $Ti_xSi_yN_z$ からなる金属膜であることを特徴とする、請求項2に記載の半導体装置の配線構造。

#### 【請求項7】

前記キャップ膜は、 $W_x N_y$  または $W_x S i_y N_z$  からなる金属膜であることを特徴とする、請求項2に記載の半導体装置の配線構造。

#### 【請求項8】

前記キャップ膜は、前記配線膜及び前記バリア膜の前記界面よりも突出した部分に選択 的に形成されていることを特徴とする、請求項1に記載の半導体装置の配線構造。

#### 【請求項9】

前記キャップ膜は、Wを主成分とする金属膜であることを特徴とする、請求項8に記載の半導体装置の配線構造。

## 【請求項10】

前記第1絶縁膜は、前記界面から突出した複数の突起部を有しており、前記突起部に前記溝部が形成されていることを特徴とする、請求項1に記載の半導体装置の配線構造。

#### 【請求項11】

前記配線膜及び前記バリア膜の上面は前記溝部の上端に略一致することを特徴とする、 請求項10に記載の半導体装置の配線構造。

## 【請求項12】

前記突起部は、前記キャップ膜をマスクとして第1絶縁膜をエッチングすることにより 形成され、前記キャップ膜は、前記突起部の上面の形状に略一致していることを特徴とす る、請求項11に記載の半導体装置の配線構造。

#### 【請求項13】

前記キャップ膜は、TaxNy、Ta又はTaxSiyNzからなることを特徴とする 、請求項12に記載の半導体装置の配線構造。

### 【請求項14】

前記キャップ膜は、 $Ti_xN_y$ 又は $Ti_xSi_yN_z$ からなる金属膜であることを特徴とする、請求項12に記載の半導体装置の配線構造。

### 【請求項15】

前記キャップ膜は、 $W_x$   $N_y$  または $W_x$  S i y  $N_z$  からなる金属膜であることを特徴とする、請求項12に記載の半導体装置の配線構造。

### 【請求項16】

前記キャップ膜は、Six Ny、Six Oy Nz、Six Cy 又はSix Cy を主成分とする絶縁膜であることを特徴とする、請求項12に記載の半導体装置の配線構造。

### 【請求項17】

第1 絶縁膜上に複数の溝部を形成するステップと、

前記第1絶縁膜上にバリア膜及び配線膜を順に形成するステップと、

前記第1:絶縁膜が露出するまで前記配線膜及びバリア膜を平坦化して、前記溝部内にの み前記配線膜及び前記バリア膜を残すステップと、

前記第1絶縁膜を薄膜化して、前記配線膜及び前記バリア膜を前記第1絶縁膜の界面よりも突出させるステップと、

前記第1絶縁膜を薄膜化した後、前記溝部ごとに分離されたキャップ膜を形成するステップと、を含むことを特徴とする半導体装置の配線構造の製造方法。

### 【請求項18】

前記配線膜及びバリア膜を平坦化するステップは、

前記バリア膜をストッパーとして前記配線膜を研磨するステップと、

前記第1絶縁膜をストッパーとして前記配線膜及び前記バリア膜を研磨するステップと、を含むことを特徴とする請求項17に記載の半導体装置の配線構造の製造方法。

## 【請求項19】

前記キャップ膜を形成するステップは、

前記第1絶縁膜を薄膜化した後、全面にキャップ膜を形成するステップと、

前記溝部の間において前記キャップ膜の一部を除去して、前記キャップ膜を前記溝部ごとに分離するステップと、

を含むことを特徴とする請求項17に記載の半導体装置の配線構造の製造方法。

### 【請求項20】

前記キャップ膜を形成するステップでは、前記配線膜及び前記バリア膜の前記界面より も突出した部分に前記キャップ膜を選択的に形成し、前記溝部ごとに分離されたキャップ 膜を形成することを特徴とする、請求項17に記載の半導体装置の配線構造の製造方法。

## 【請求項21】

前記キャップ膜はタングステンWであることを特徴とする、請求項20に記載の半導体装置の配線構造の製造方法。

#### 【請求項22】

第1絶縁膜上に複数の溝部を形成するステップと、

前記第1絶縁膜上にバリア膜及び配線膜を順に形成するステップと、

前記第1絶縁膜の表面が露出するまで配線膜及びバリア膜を平坦化し、前記溝部内にの み配線膜及びバリア膜を残すステップと、

前記配線膜及び前記バリア膜の平坦化の後、全面にキャップ膜を形成するステップと、 少なくとも前記配線膜及び前記バリア膜上に前記キャップ膜が残るように前記キャップ 膜を除去するステップと、

前記第1絶縁膜を前記キャップ膜が除去された部分において薄膜化し、前記薄膜化された部分の第1絶縁膜の界面よりも前記配線膜及び前記バリア膜を突出させるステップと、を含むことを特徴とする半導体装置の配線構造の製造方法。

#### 【請求項23】

前記キャップ膜を除去するステップでは、前記配線膜及び前記バリア膜上にのみ前記キャップ膜が残るように前記キャップ膜を除去することを特徴とする、請求項22に記載の 半導体装置の配線構造の製造方法。

#### 【請求項24】

前記配線膜及びバリア膜を平坦化するステップは、

前記バリア膜をストッパーとして前記配線膜を研磨するステップと、

前記第1絶縁膜をストッパーとして前記配線膜及び前記バリア膜を研磨するステップと、を含むことを特徴とする請求項22に記載の半導体装置の配線構造の製造方法。

## 【請求項25】

)

前記第1絶縁膜を薄膜化するステップは、少なくとも前記配線膜及び前記バリア膜上に 残った前記キャップ膜をマスクとして、前記第1絶縁膜を加工することを特徴とする、請 求項22に記載の半導体装置の配線構造の製造方法。

## 【請求項26】

溝部が形成された突起部を複数有するとともに、隣接する突起部の間に水平方向の界面 を有する第1絶縁膜と、

前記溝部にバリア膜を介して埋め込まれた複数の配線膜と、

前記突起部の上面に形成された複数の第1キャップ膜と、

前記第1キャップ膜及び前記第1絶縁膜上に形成された第2キャップ膜と、

を備えることを特徴とする半導体装置の配線構造。

### 【請求項27】

前記配線膜及び前記バリア膜の上面は前記溝部の上端に略一致することを特徴とする、 請求項26に記載の半導体装置の配線構造。

## 【請求項28】

前記突起部は、前記第1キャップ膜をマスクとして第1絶縁膜をエッチングすることにより形成され、前記第1キャップ膜は、前記突起部の上面の形状に略一致していることを特徴とする、請求項26に記載の半導体装置の配線構造。

### 【請求項29】

前記第1キャップ膜は、TaxNy、Ta又はTaxSiyNzからなる金属膜であることを特徴とする、請求項28に記載の半導体装置の配線構造。

#### 【請求項30】

前記第1キャップ膜は、 $Ti_xN_y$ 又は $Ti_xSi_yN_z$ からなる金属膜であることを特徴とする、請求項28に記載の半導体装置の配線構造。

#### 【請求項31】

前記第1キャップ膜は、 $W_x$   $N_y$  または $W_x$  S  $i_y$   $N_z$  からなる金属膜であることを特徴とする、請求項2 8 に記載の半導体装置の配線構造。

## 【請求項32】

前記第2キャップ膜は、SixNy、SixOyNz、SixCy又はSixCyを主成分とする絶縁膜であることを特徴とする、請求項28に記載の半導体装置の配線構造。

### 【書類名】明細書

【発明の名称】半導体装置の配線構造及びその製造方法

### 【技術分野】

)

### $[0\ 0\ 0\ 1]$

本発明は、半導体装置の配線構造及びその製造方法に関する。

### 【背景技術】

### [0002]

半導体装置の微細化に伴い、R C 遅延(抵抗値及び容量値による信号遅延)の影響が大きくなり、半導体装置の高速化を妨げる重要な原因となっている。配線の抵抗値及び配線間の容量を低減するために、配線幅  $0.25\mu$  m以下の半導体装置では、アルミニウム合金に代わって銅C u を用いた配線が導入されている。C u を用いた配線の形成では、一般的にドライエッチングが困難なため、絶縁膜に形成された配線溝にC u を堆積させた後に平坦化するダマシン法が用いられている。ダマシン法により形成された従来のC u 配線の構造が、例えば、特許文献 1 乃至 6 に記載されている。

## [0003]

特許文献1及び2に記載のCu配線構造では、第1の絶縁膜(シリコン酸化膜)に複数の配線溝が形成されており、これらの配線溝には、Cuの酸化及び拡散防止のためのバリア膜を介してCu配線膜が形成されている。Cu配線膜及びバリア膜は、第1絶縁膜の界面と一致するように平坦化されている。

### [0004]

特許文献 3 及び 4 に記載の C u 配線構造では、第 1 絶縁膜に形成された配線溝に、バリア膜を介して C u 配線膜が配線溝の深さよりも浅く埋め込まれており、 C u 配線膜の上には、 C u の酸化及び拡散防止のための金属膜や窒化膜からなるキャップ膜が配線溝に埋め込まれている。

### [0005]

特許文献5に記載のCu配線構造では、第1絶縁膜の配線溝にバリア膜を介してCu配線膜が埋め込まれており、バリア膜が配線溝の上端と一致する高さまで形成されており、Cu配線膜は配線溝よりも凸状に突出している。また、配線溝から突出したCu配線膜の上から全面に第2の絶縁膜(酸化膜)が形成されている。

### [0006]

特許文献6に記載されたCu配線構造では、第1絶縁膜の配線溝にバリア膜を介してCu配線膜が埋め込まれており、Cu配線膜及びバリア膜が配線溝よりも凸状に突出している。また、Cu配線膜及びバリア膜の突出した部分を覆うように全面にキャップ膜が形成されている。

【特許文献1】特開平10-270448号公報(第2頁、第3図)

【特許文献2】特開2001-358105号公報(第4-6第2図)

【特許文献3】特開平6-120219号公報(第2-3頁、第2図)

【特許文献4】特開平10-261635号公報(第3-6頁、第1図)

【特許文献 5】 特開平 1 0 - 1 8 9 5 9 0 号公報 (第 5 - 6 頁、第 1 0 図)

【特許文献6】特開2002-329780号公報(第15頁、第20図)

#### 【発明の開示】

【発明が解決しようとする課題】

### [0007]

特許文献1及び2に記載のCu配線構造では、配線材料のリーク源となるCu配線膜の上面と、リーク電流のパスとなる第1絶縁膜の界面とが連続しているので、Cu配線膜の上面縁部から配線材料のCuイオンが第1絶縁膜の界面を介して拡散してリーク電流が流れたり、Cu配線膜の上面縁部からCuヒロックが第1絶縁膜の界面を介して拡大し、配線間が電気的に短絡する虞がある。

### [0008]

特許文献3及び4に記載のCu配線構造では、配線材料のリーク源となるCu配線膜の

上面はリーク電流のパスとなる第1絶縁膜の界面よりも低く、配線材料のリーク源とリーク電流のパスとが上下に離れているが、配線溝内に埋め込まれるキャップ膜の膜厚分だけ配線溝を深くする必要があり、配線幅の微細化に伴い配線溝のアスペクト比が増大し、配線膜の形成が困難になる虞がある。また、必要なキャップ膜の膜厚に応じてCu配線膜の窪みの量を調整する必要があるが、各種配線幅、配線密度の存在するパターンにおいてCu配線膜の窪み量を精度良く制御することは困難であり、ウエハ内でCu配線膜の膜厚が均一とならず配線抵抗がばらつく原因となる。

## [0009]

特許文献5に記載のCu配線構造では、第2絶縁膜とバリア膜との界面がCu配線膜と接触しているため、Cu配線膜からこの界面を介してCuイオンが拡散したり、Cuヒロックが拡大する虞がある。

### $[0\ 0\ 1\ 0\ ]$

特許文献6に記載のCu配線構造では、配線材料のリーク源であるCu配線膜の上面縁部と、リーク電流のパスとなる第1絶縁膜の界面とが上下方向に分離されているが、誘電率の高いキャップ膜が全面に形成されており、多層配線構造では層間の配線間容量が大きくなり、半導体素子の高速動作の妨げとなる虞がある。

### $[0\ 0\ 1\ 1]$

また、特許文献5及び6に記載したようなCu配線構造では、第1絶縁膜の上面が配線膜の上面よりも低くなるように第1絶縁膜を薄膜化する際にCu配線膜の一部が除去されてしまう虞があり、配線抵抗がばらつく原因となる。

### $[0\ 0\ 1\ 2]$

本発明は、半導体装置の配線構造において、配線材料の拡散を防止することにより配線の絶縁耐性を向上させるとともに、配線間容量を低減することにある。

### [0013]

また、本発明の別の目的は、半導体装置の配線構造において、配線材料の拡散を防止することにより配線の絶縁耐性を向上させるとともに、配線膜の抵抗のばらつきを抑制することを目的とする。

#### 【課題を解決するための手段】

#### [0014]

本発明に係る配線構造は、第1絶縁膜と、複数の配線膜と、複数のバリア膜と、複数のキャップ膜とを備えている。第1絶縁膜には、複数の溝部が形成されている。また、第1絶縁膜は、隣接する溝部の間に水平方向の界面を有している。配線膜は、第1絶縁膜の溝部ごとに上記界面よりも突出して形成されている。バリア膜は、配線膜の底面に形成されるとともに、配線膜の側面において上記界面より上方まで形成されている。キャップ膜は、少なくとも配線膜の上面に形成されており、溝部ごとに分離されている。

#### $[0\ 0\ 1\ 5]$

別の本発明に係る半導体装置の配線構造の製造方法は、第1絶縁膜上に複数の溝部を形成するステップと、第1絶縁膜上にバリア膜及び配線膜を順に形成するステップと、第1絶縁膜の表面が露出するまで配線膜及びバリア膜を平坦化し、溝部内にのみ配線膜及びバリア膜を残すステップと、配線膜及びバリア膜の平坦化の後、全面にキャップ膜を形成するステップと、少なくとも前記配線膜及びバリア膜上にキャップ膜が残るようにキャップ膜を除去するステップと、第1絶縁膜をキャップ膜が除去された部分において薄膜化し、薄膜化された部分の第1絶縁膜の界面よりも配線膜及びバリア膜を突出させるステップと、を含むことを特徴とする。

#### 【発明の効果】

### [0016]

本発明に係る半導体装置の配線構造では、配線材料のリーク源となる配線膜の上面縁部と、配線材料によるリーク電流のパスとなる第1絶縁膜の界面とが上下方向に離れているので、配線材料がリークしたとしてもリーク電流のパスとなる第1絶縁膜の界面に到達し難く、配線材料の拡散を防止することができる。また、キャップ膜が溝部ごとに分離され

3/

ているので、キャップ膜に誘電率の高い材料を用いたとしても、配線間容量の増大を抑制 することができる。このように、本発明に係る半導体装置の配線構造によれば、配線の絶 縁耐性を向上させるとともに、配線容量の低減を図ることができる。

### $[0\ 0\ 1\ 7]$

別の本発明に係る半導体装置の配線構造の製造方法によれば、配線材料のリーク源となる配線膜の上面縁部と、配線材料によるリーク電流のパスとなる第1絶縁膜の界面とが上下方向に離れているので、配線材料がリークしたとしてもリーク電流のパスとなる第1絶縁膜の界面に到達し難く、配線材料の拡散を防止することができる。また、少なくとも配線膜及びバリア膜上にキャップ膜を残して、このキャップ膜をマスクとして絶縁膜の薄膜化を行うので、第1絶縁膜の薄膜化の際に配線膜の一部が除去されることを防止でき、配線膜の抵抗のばらつきを抑制できる。

【発明を実施するための最良の形態】

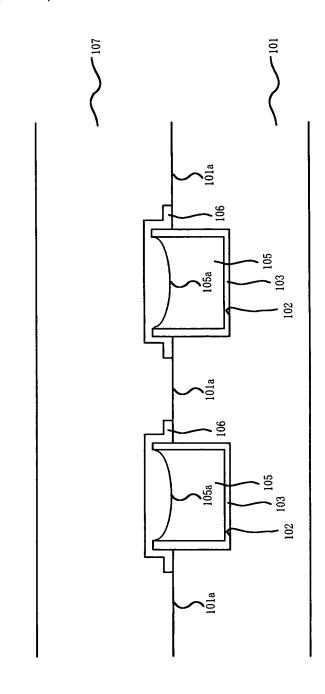

## [0018]

(1) 第1 実施形態

#### 〔構造〕

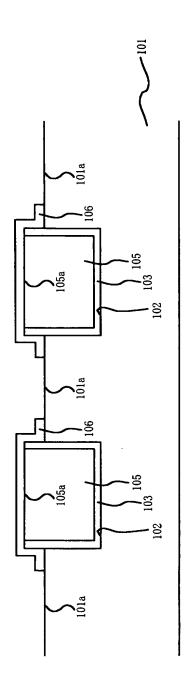

図10は、本発明の第1実施形態に係る配線構造の断面図である。この配線構造は、第1の絶縁膜101と、複数のバリア膜103と、複数の配線膜105と、複数のキャップ膜106と、第2の絶縁膜107と、を備えている。絶縁膜101には複数の溝部102が形成されている。また、絶縁膜101は、隣接する溝部102の間に水平方向の上面としての界面101aを有している。配線膜105は、絶縁膜101の溝部102ごとに界面101aよりも凸状に突出して形成されている。バリア膜103は、配線膜105の底面に形成されるとともに、配線膜105の側面において界面101aより上方まで形成されている。キャップ膜106は、少なくとも配線膜105の上面に形成されており、溝部102ごとに分離されている。絶縁膜107は、キャップ膜106及び絶縁膜101上に形成されている。

### [0019]

〔製造方法〕

以下、配線構造の製造方法を図1から図9を参照して説明する。

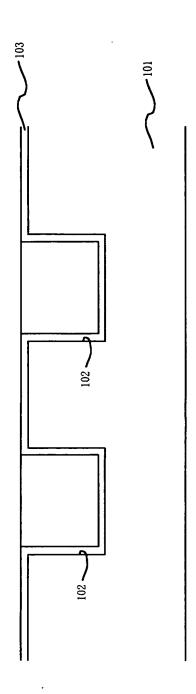

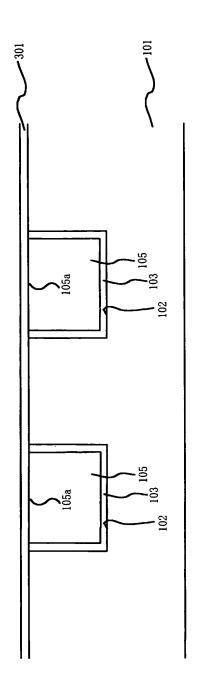

#### [0020]

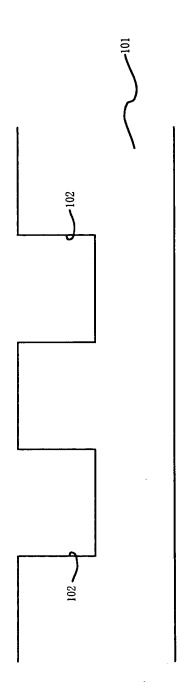

図1に示すように、半導体素子が形成された基板(図示せず)の上に、CVD法により、酸化シリコンSiO2からなる膜厚500nmの絶縁膜101を形成し、ホトリソグラフィー及びエッチングにより、配線形成予定領域(配線パターンを形成する領域)に複数の溝部102を形成する。溝部102は、幅200nm、深さ350nmであり、隣接する溝部102の間隔は200nmである。溝部102のエッチングは、例えば、マグネトロン型反応性イオンエッチング(RIE: Reactive Ion Etching)装置を用いる。なお、絶縁膜101のエッチングは、マグネトロン型カソードカップルエッチング装置、二周波励起容量結合プラズマエッチング装置、ICP(Inductive coupled plasma)型エッチング装置のなかから適宜選択されたエッチング装置を好適に用いることができる。絶縁膜101のエッチングに使用するエッチングガスは、例えば、オクタフルオロシクロブタンC4F8と一酸化炭素COと酸素O2とアルゴンArとを使用する。エッチングの条件は、例えば、ガス流量C4F8/CO/O2/Ar=14/50/5/30sccm、RFパワー1.5kW、チャンバー圧力50mTorrとする。

### $[0\ 0\ 2\ 1]$

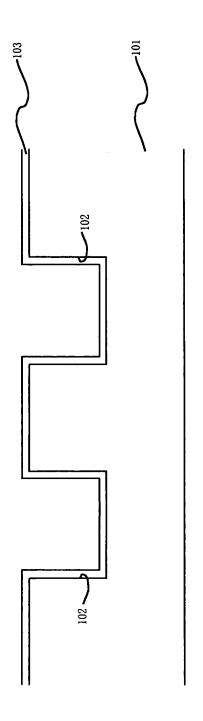

えばTa、TaxSiyNz、TixNy、TixSiyNz、WxNy、WxSiyNzを用いて良い。

## [0022]

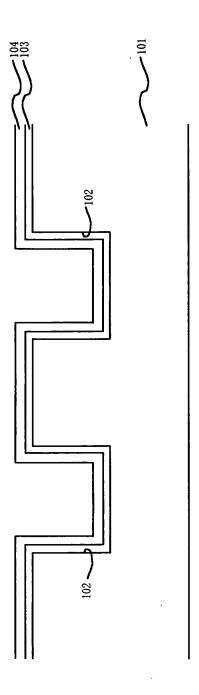

次に、図3に示すように、バリア膜103の表面にメッキ膜の種となる膜厚150nmのCuシード膜104を形成する。Cuシード膜104の形成では、例えば、ターゲットにCu、プロセスガスにArを用い、雰囲気の圧力を2mTorr、成膜温度を30℃、DCパワーを12kWの条件で、指向性の高いスパッタリングによりCuを堆積する。なお、Cuシード膜104は、CuまたはCuを主成分とする合金であっても良い。

### [0023]

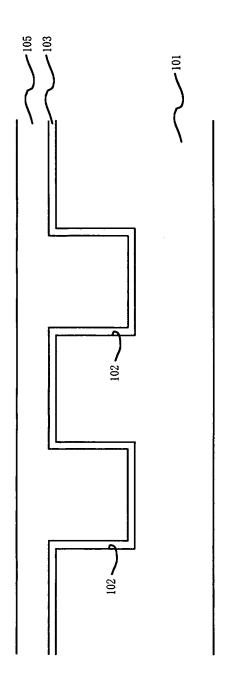

次に、図4に示すように、Cuシード膜104の表面に電界メッキ法によりCuからなる配線膜105を堆積する。配線膜105は、溝部102を埋め尽くす膜厚以上だけ堆積すれば良いが、ここでは、配線膜105を絶縁膜101の表面よりも数百nm高い位置まで堆積する。電界メッキには、例えば、Cu成分を析出させる元になる硫酸銅CuSO4・5H2O、電導性を高めるための硫酸H2SO4、高電流密度部の光沢性や溶解性アノード(例えば、リン含有銅)の溶解を促進するための塩素Cl、埋込性を向上させる添加剤などを含むメッキ液を使用する。電界メッキは、例えば、上記メッキ液を用いて、液温25℃、定電流の条件で、電流密度を2段階に切り換えて行う。電流密度の切換えは、例えば、第1段階では低電流密度0.2A/dm²とし、第2段階では高電流密度2A/dm²とする。このように電流密度を2段階に変化させる理由は、高電流密度のみで電界メッキを実行すると、微細パターンである溝部102の入り口でメッキ膜(配線膜105)が閉じてしまいボイドが形成される虞がある一方、低電流密度のみで電界メッキを実行すると、配線膜105の堆積速度が遅く、溝部102の埋め込みに時間を要するからである。以下の説明では、Cuシード膜104も含めて配線膜105と称す。

## [0024]

配線膜105を電界メッキした後、炉内にて例えば温度100~350℃、窒素N2及び水素H2の混合雰囲気中で1~300分間の熱処理を行う。或いは、基板をホットプレートに戴載して熱処理しても良い。この熱処理により、配線膜105の微細なCu結晶粒の成長を促すとともに、膜の硬度、結晶性、比抵抗等の安定化を図る。

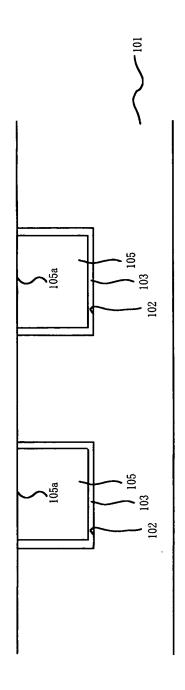

#### $[0\ 0\ 2\ 5]$

次に、図5及び図6に示すように、配線膜105、バリア膜103をCMP法により研磨し、配線膜105及びバリア膜103を平坦化する。より詳細には、絶縁膜101が露出するまで配線膜105、バリア膜103を除去して、配線膜105及びバリア膜103を溝部102内にのみ残す。この結果、配線膜105及びバリア膜103の上面が絶縁膜101の表面と一致するようになる。105aは、配線膜105の上面である。

## [0026]

このCMPによる研磨は、例えば2段階の研磨を含んでいる。第1段階では、バリア膜103をストッパーにして、絶縁膜101の表面にあるバリア膜103の表面が露出するまで配線膜105を研磨、除去する(図5)。第1段階では、研磨粒子としてシリカを含む溶液に銅錯体形成促進剤として過酸化水素 $H_2O_2$ を加えたものをスラリーとして使用する。また、研磨パッドには、不織布と独立発砲体の積層構造を用い、スラリー流量200ml/min、研磨荷重2psi、キャリアヘッド回転数120rpm、テーブル回転数120rpmとする。続いて第2段階では、絶縁膜101をストッパーにして、絶縁膜101の表面にあるバリア膜103を除去する(図6)。第2段階でも、研磨粒子としてシリカを含む溶液に過酸化水素 $H_2O_2$ を加えたものをスラリーとして使用する。また、研磨パッドには、不織布と独立発泡体の積層構造を用い、スラリー流量200ml/min、研磨荷重2psi、キャリアヘッド回転数80rpmとする。

### [0027]

なお、配線膜105及びバリア膜103の平坦化では、理想的には、配線膜105及び バリア膜103の上面が一致することが好ましいが、実際には、図6に示すバリア膜10 3を除去する際(第2段階の研磨)に、図19に示すように溝102内の配線膜105がバリア膜103よりも研磨されるディッシングが発生するため、配線膜105の上面105aの中央部がバリア膜103の上面に対して5nm~10nmだけ窪む。この場合にも、CuイオンやCuヒロックのリーク源となる配線膜105の上面105aは、後述する絶縁膜101の薄膜化によって絶縁膜101の界面101aよりも突出する。

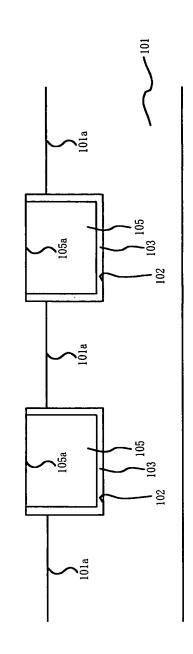

## [0028]

次に、図7に示すように、絶縁膜101を表面から例えば50nm除去して薄膜化する。絶縁膜101の薄膜化は、CMP法による研磨を使用しても良いし、フッ酸(0.3% HF等)によりエッチバックしても良い。絶縁膜101の薄膜化により、バリア膜103及び配線膜105は、絶縁膜101の表面よりも凸状に突出する。

### [0029]

続いて、図8に示すように、絶縁膜101の表面及び配線膜105を覆うように、タンタルTaからなる膜厚50nmのキャップ膜106を堆積する。キャップ膜106の形成は、例えば、ターゲットにTa、プロセスガスにアルゴンArを用い、雰囲気の圧力を3mTorr、成膜温度を150℃、DCパワーを6kWの条件で、指向性を高めたスパッタリングにより行う。キャップ膜106は、金属膜である配線膜105及びバリア膜103との密着性を高めるために、金属元素を含んだ膜であることが望ましい。配線膜105及びバリア膜103とキャップ膜106との密着性を改善により、Сиイオンの拡散を抑制できるとともに、ヒロックの発生も抑制することができる。また、Сиイオンの拡散及びСиヒロックの拡大等のСи拡散のリーク源となる配線膜105の上面105aと、配線膜105間でのリーク電流のパスとなる絶縁膜101の界面101aとをから上下方向で分離することにより、バリア膜103の上面にСиが拡散したとしても絶縁膜101の界面101aまで到達し難く、リーク電流を抑制するとともに、配線膜105間での短絡を防止できる。

## [0030]

また、キャップ膜 106 は、TaxNy、TaxSiyNz 等のタンタルを主成分とする金属膜、TixNy、TixSiyNz 等のチタンを主成分とする金属膜、または、WxNy、WxSiyNz 等のタングステンを主成分とする金属膜等の導電膜によって形成しても良い。また、キャップ膜 106 は、SixNy、SixOyNz、SixCy、ZixCy を主成分とする絶縁膜を用いることもできる。キャップ膜 106 を絶縁膜で形成した場合、Cu イオンの拡散及びCu ヒロックの発生が生じやすいバリア膜 103 の上面の側方が絶縁膜で覆われることになり、さらに配線膜間でのリーク電流を抑制し、配線間での電気的な短絡を抑制し得る。

#### $[0\ 0\ 3\ 1]$

次に、図9に示すように、ホトリングラフィー及びエッチング技術により、配線膜105の間、即ち絶縁膜101の界面101a上にあるキャップ膜106を取り除き、キャップ膜106を配線膜105ごとに分離する。次に、図10に示すように、CVD法により、酸化シリコンSiO2からなる膜厚700nmの絶縁膜107を堆積する。

## [0032]

〔作用効果〕

本実施形態に係る配線構造によれば、配線膜105及びバリア膜103が溝部102よりも凸状に突出するように形成されており、配線材料Cuのリーク源となる配線膜105の上面105aの縁部と、配線材料によるリーク電流のパスとなる界面101aとが上下方向に離れているので、配線材料Cuが配線膜105からリークしたとしてもリーク電流のパスとなる界面101aに到達し難く、配線材料Cuの拡散を抑制することができる。

## [0033]

比誘電率の高い材料を用いてキャップ膜106を全面に形成する場合には、配線間容量の増大が問題となる。特に、多層配線構造においては、層間での配線間容量が増大し、信号遅延の要因となる虞がある。これに対して、本実施形態のようにキャップ膜106を溝部102ごとに分離すれば、層間の絶縁材料であるキャップ膜106及び絶縁膜107全

体での比誘電率、即ち実効比誘電率を低減することができるので、層間での配線間容量を抑制することができる。特に、キャップ膜106 を比誘電率7.00 S i x N y で形成する場合には、比誘電率4.2 の酸化シリコン S i O 2 で形成する絶縁膜107 よりも大幅に大きいため、比誘電率の高いキャップ膜106 の体積を減少させれば、層間の配線間容量を大幅に低減することができる。

### [0034]

また、配線間容量の低減するためには、絶縁膜107の材料として、低比誘電率のフッ素ドープのSiO₂(FSG膜、比誘電率3.5程度)などを使用する場合があるが、絶縁膜107の比誘電率が低下するほどキャップ膜106が実効誘電率に与える影響が大きくなるので、本実施形態で示したようにキャップ膜を溝部102ごとに分離する構成は実効誘電率の低減に有効である。

### [0035]

以上のように、本実施形態に係る半導体装置の配線構造によれば、配線材料Cuの拡散を抑制することにより配線間の絶縁耐性を向上させるとともに、配線間容量を低減することができる。

### [0036]

なお、図6に示す工程において配線膜105及びバリア膜103をCMP法により研磨して平坦化する際には、図19に示すように、配線膜105の上面105aの中央部がバリア膜103の上面よりも5nm~10nm窪むことがある。このような場合であっても、CuイオンやCuヒロックのリーク源となる配線膜105の上面105aは、リーク電流のパスとなる絶縁膜101の界面101aよりも上方に突出し、配線膜105の上面105aの縁部と界面101aとが上下方向に分離されているので、配線膜105の上面105aからCuイオン又はCuヒロックが絶縁膜101の界面101aに到達し難い。

## [0037]

また、上記では、キャップ膜 106 を界面 101 a 上で分離したが、図 20 に示すように配線膜 105 及びバリア膜 103 の上面のみにキャップ膜 106 が残るようにしても良い。図 20 のようにキャップ膜 106 を形成すれば、キャップ膜 106 が導電膜である場合には隣接するキャップ膜 106 間の距離、即ち実質的な配線間距離が増大することにより絶縁耐性をさらに向上させることができる。また、キャップ膜 106 が高誘電率の絶縁膜である場合には、実効誘電率をさらに低減させることができる。なお、キャップ膜 106 の位置合わせがずれてバリア膜 103 の上面の一部がキャップ膜 106 で覆われない場合もあるが、配線膜 105 の上面がキャップ膜 106 に覆われていれば配線膜 105 の酸化を防止できるため問題ない。

#### [0038]

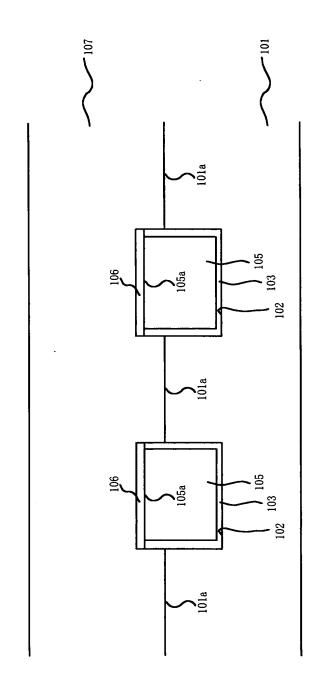

(2) 第2実施形態

#### 〔構造〕

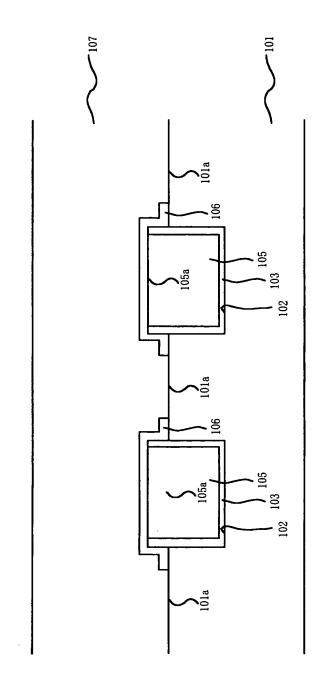

図12は、本発明の第2実施形態に係る配線構造の断面図である。この配線構造は、第1の絶縁膜101と、複数のバリア膜103と、複数の配線膜105と、複数のキャップ膜201と、第2の絶縁膜202とを備えている。絶縁膜101には複数の溝部102が形成されている。また、絶縁膜101は、隣接する溝部102の間に水平方向の上面としての界面101aを有している。配線膜105は、絶縁膜101の溝部102ごとに界面101aよりも凸状に突出して形成されている。バリア膜103は、配線膜105の底面に形成されるとともに、配線膜105の側面において界面101aより上方まで形成されている。キャップ膜201は、配線膜105及びバリア膜103の上記界面101aよりも突出した部分に選択的に形成されている。絶縁膜107は、キャップ膜201及び絶縁膜101上に形成されている。

### [0039]

〔製造方法〕

以下、第2実施形態に係る配線構造の製造方法を図11及び図12を参照して説明する

## [0040]

第1実施形態に係る図1乃至図7の工程を経た後、図11に示すように、界面101aから凸状に突出している配線膜105及びバリア膜103上にタングステンWからなる膜厚30nmのキャップ膜201を選択的に形成する。タングステンWによるキャップ膜201の形成の前処理としては、水素H2を含む雰囲気で熱処理を行い、Cuからなる配線膜105の表面にある酸化膜を除去する。この熱処理の条件は、例えば、基板温度350℃、H2流量1000sccm、Ar流量300sccm、圧力1Torr、処理時間60sec~300secとする。この熱処理に引き続いて真空を破ることなく、タングステンW膜形成用のチャンバーに基板(ウエハの状態)を搬送し、タングステンWからな、膜厚30nmのキャップ膜201を選択的に堆積する。タングステンW膜の形成条件は、例えば、基板温度200~300℃、WF6流量5sccm、H2流量500sccm、圧力300mTorrとする。金属であるタングステンWは、金属膜である配線膜105及びバリア膜103上に選択的に堆積される。より詳細には、タングステンWは、配線膜105の上面とバリア膜103の上面及び側面とに選択的に堆積される。なお、ここでは、タングステンW膜形成の前処理(熱処理)とタングステンW膜の形成とを別々のチャンバーで行っているが、これらの処理を同一チャンバー内で行っても良い。

### $[0\ 0\ 4\ 1\ ]$

配線膜 105 及びバリア膜 103 にキャップ膜 201 を選択的に形成した後、第1実施形態と同様に、CVD法により、絶縁膜 101 及びキャップ膜 201 を覆うように、酸化シリコンS i02 からなる膜厚 700 n m の絶縁膜 202 を堆積する(図 12)。

### [0042]

### [作用効果]

本実施形態に係る配線構造では、第1実施形態と同様に、配線材料Cuのリーク源である配線膜105の上面と、リーク電流のパスとなる界面101aとが上下方向に分離されているため、配線材料Cuが配線膜105からリークしたとしてもリーク電流のパスとなる界面101aに到達し難く、配線材料Cuの拡散を抑制することができる。

#### $[0\ 0\ 4\ 3]$

また、配線膜 105の上面 105 a が金属膜からなるキャップ膜 201 に接触するので、配線膜 105 とキャップ膜 201 との密着性が良く、上面 105 a におけるエレクトロマイグレーションの発生を抑制することができる。このため、配線膜 105 的の配線材料のリーク自体を抑制することができ、配線膜 105 間の絶縁耐性をさらに向上させることができる。

#### $[0\ 0\ 4\ 4]$

また、配線膜 105 間では、キャップ膜 201 を介さずに絶縁膜 101 と絶縁膜 202 とが直接密着する。絶縁膜 101 と絶縁膜 202 との間に金属膜であるキャップ膜 201 が介装されると、絶縁膜 101 とキャップ膜 201 との密着性が悪くなるが、絶縁膜 101 と絶縁膜 202 とを直接密着させることにより、絶縁膜 101 と絶縁膜 202 との密着性を向上させることができる。

### [0045]

また、本実施形態では、タングステンWからなるキャップ膜201を配線膜105及びバリア膜103上に選択的に形成して溝部102ごとに分離されたキャップ膜201を形成することができるので、キャップ膜を溝部102ごとに分離するためのホトリソグラフィー及びエッチングを省略することができ、製造工程を簡略化することができる。

### [0046]

#### (3) 第3実施形態

本実施形態に係る半導体装置の配線構造では、本発明の別の目的を解決することを目的とする。即ち、背景技術において特許文献5及び6に記載したようなCu配線構造では、第1絶縁膜の上面がCu配線膜の上面よりも低くなるように第1絶縁膜を薄膜化する際にCu配線膜の一部が除去されてしまう虞があり、配線抵抗がばらつく原因となる。そこで、半導体装置の配線構造において、配線材料の拡散を防止することにより配線の絶縁耐性

を向上させるとともに、配線膜の抵抗のばらつきを抑制することを目的とする。

### [0047]

〔構造〕

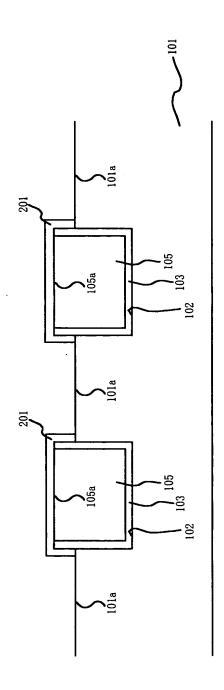

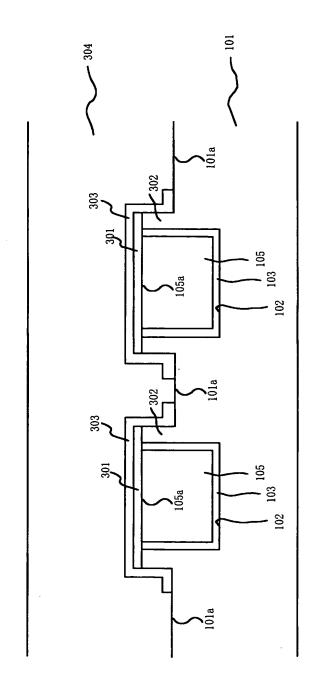

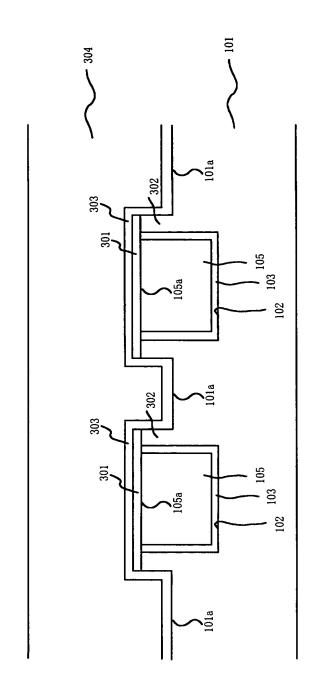

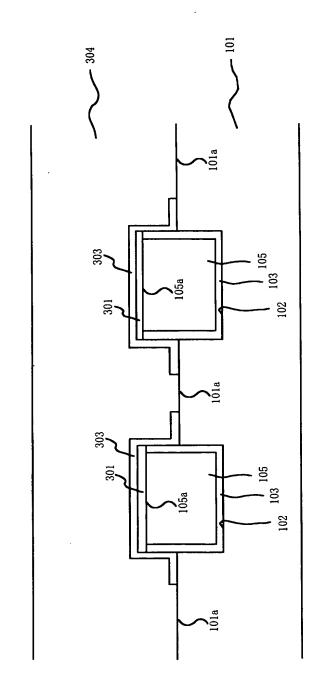

図17は、本発明の第3実施形態に係る配線構造の断面図である。この配線構造は、複 数の突起部302が形成された第1の絶縁膜101と、複数のバリア膜103と、複数の 配線膜105と、複数の第1のキャップ膜301と、複数の第2のキャップ膜303と、 第2の絶縁膜304とを備えている。

### [0048]

絶縁膜101には複数の溝部102が形成されている。また、絶縁膜101は、隣接す る溝部102の間に水平方向の上面としての界面101aを有している。また、絶縁膜1 01は、界面101aから突出して形成された複数の突起部302を有している。配線膜 105は、絶縁膜101の溝部102ごとに界面101aよりも凸状に突出して形成され ている。バリア膜103は、配線膜105の底面に形成されるとともに、配線膜105の 側面において界面101aより上方まで形成されている。配線膜105及びバリア膜10 3の上面は、溝部102の上端と略一致するように形成されている。キャップ膜301は 、絶縁膜101をエッチングして突起部302を形成する際のエッチングマスクとして用 いられる。キャップ膜303は、キャップ膜301及び突起部302を覆うように形成さ れている。絶縁膜303は、キャップ膜303及び絶縁膜101を覆うように形成されて いる。

### [0049]

なお、理想的には、配線膜105及びバリア膜103の上面が一致することが好ましい が、実際には、第1実施形態でも述べたように、バリア膜103を除去する際(第2段階 の研磨)に、溝102内の配線膜105がバリア膜103よりも研磨されるディッシング が発生するため、配線膜105の上面105aの中央部がバリア膜103の上面に対して 5 nm~10 nmだけ窪む。この場合にも、CuイオンやCuヒロックのリーク源となる 配線膜105の上面105aは、後述する絶縁膜101の薄膜化によって絶縁膜101の 界面101aよりも突出する。

### [0050]

〔製造方法〕

以下、第3実施形態に係る配線構造の製造方法を図13乃至図17を参照して説明する

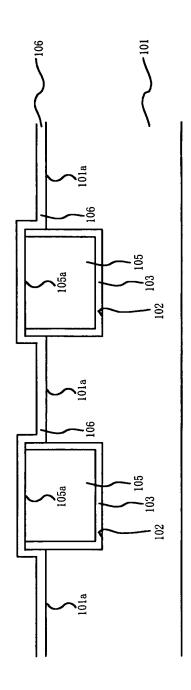

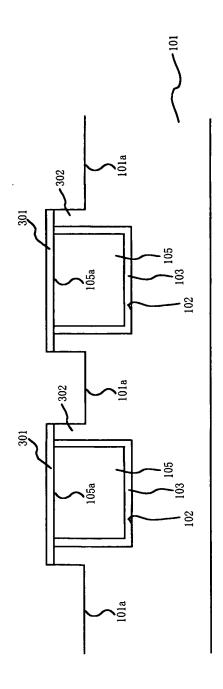

#### $[0\ 0\ 5\ 1]$

第1実施形態に係る図1乃至図6の工程を経て、溝部102に配線膜105及びバリア 膜103が埋め込まれた絶縁膜101の上に、図13に示すように、窒化チタンTixN vからなる膜厚50nmのキャップ膜301を形成する。キャップ膜301は、Ta、T a x N v 、 T a x S i y N z 等の T a を主として含む合金、 T i x S i y N z 等の T i を 主として含む合金、Wx Ny 、Wx Siy Nz 等のWを主として含む合金等の導電体でも 良い。

### $[0\ 0\ 5\ 2]$

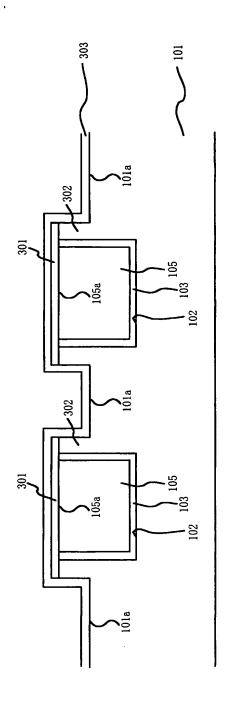

次に、図14に示すように、ホトリソグラフィー及びエッチングにより、溝部102の 周囲の領域以外の部分のキャップ膜301を除去し、キャップ膜301が除去された部分 の絶縁膜101を薄膜化する。これにより、絶縁膜101には、溝部102の周囲に残っ た絶縁膜101が突起部302を形成する。キャップ膜301のエッチング(第1のエッ チング)の条件は、例えば、エッチングガスとして塩素C12、三塩化ホウ素BC13を 使用し、ガス流量Cl2 /BCl3 =70/30sccm、チャンバー圧力15mTor r、RF電力12kW、バイアス電力60Wとする。絶縁膜101のエッチング(第2の エッチング)の条件は、例えば、エッチングガスとしてC4F8、CO、O2、Arを使 用し、ガス流量C4 F8 / CO/O2 / Ar = 14/50/5/30 sccm、RF電力 5kW、チャンバー圧力50mTorrとする。

## [0053]

なお、ここでは、キャップ膜301のエッチングと、絶縁膜101のエッチングとを別々に行ったが、キャップ膜301のエッチング(第1のエッチング)で絶縁膜101の薄膜化を共に行い、第2のエッチングを省略しても良い。第1のエッチングでは、化学的なエッチングで主にキャップ膜301を除去しているが、化学的なエッチングの成分に加え、表面をスパッタリングする物理的なエッチングの成分も含んでいる。従って、第1のエッチングにおいて、キャップ膜301のエッチングを過剰に行い、物理的なエッチングによって絶縁膜101も薄膜化することが可能である。

### [0054]

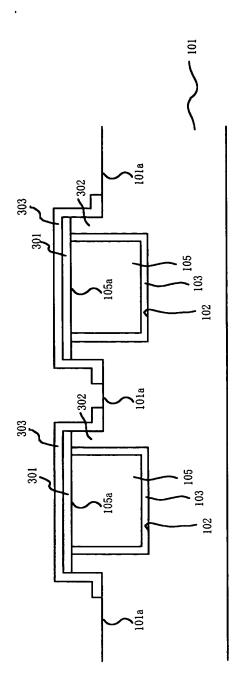

次に、図15に示すように、窒化シリコンSi $_{x}$  N $_{y}$  からなる膜厚50  $_{n}$  mのキャップ 膜303を $_{n}$  C V D 法により堆積する。次に、図16に示すように、キャップ膜303をエッチングにより溝部102ごと(突起部302ごと)に分離する。その後、図17に示すように、C V D 法により、キャップ膜303上に酸化シリコンSiO $_{2}$  からなる膜厚700  $_{n}$  mの絶縁膜304を堆積する。

### [0055]

## [作用効果]

本実施形態に係る配線構造でも、配線材料Cuのリーク源となる配線膜105の上面105aの縁部と、配線材料によるリーク電流のパスとなる界面101aとが上下方向に離れているので、配線材料Cuが配線膜105からリークしたとしてもリーク電流のパスとなる界面101aに到達し難く、配線材料Cuの拡散を抑制することにより、配線の絶縁耐性を向上させることができる。

### [0056]

また、本実施形態でも、キャップ膜301及び303を溝部102ごとに分離してるので、実効比誘電率を低減し、層間での配線間容量を抑制することができる。

### [0057]

また、本実施形態では、配線膜105がキャップ膜301で覆われた状態で絶縁膜10 1の薄膜化するため、絶縁膜101の薄膜化において、CMP法による研磨によって配線 膜105が研磨されて配線膜105の体積が減少することを防止できる。これにより、配 線膜105の抵抗のばらつきを抑制できる。

#### [0058]

また、絶縁膜101をHF処理により薄膜化する場合には、バリア膜103として一般的に使用されるTaからなる膜がエッチングされる懸念があるが、本実施形態のように配線膜105及びバリア膜103をキャップ膜301で覆った状態でエッチングする場合には、Taからなる膜がエッチングされる懸念がない。

#### [0059]

また、上記では、キャップ膜301を配線膜105及びバリア膜103よりも広く形成したが、絶縁膜101の薄膜化の際にバリア膜103がエッチングされる虞がない場合には、図21に示すように、配線膜105及びバリア膜103の上面のみにキャップ膜301が残るようにしても良い。配線膜105及びバリア膜103の上面のみにキャップ膜301を形成すれば、隣接するキャップ膜301間の距離、即ち実質的な配線間距離が増大することにより絶縁耐性をさらに向上させることができる。また、キャップ膜301の位置合わせがずれてバリア膜103の上面の一部がキャップ膜301で覆われない場合もあるが、さらにキャップ膜303で覆うため配線膜105が酸化される懸念はない。

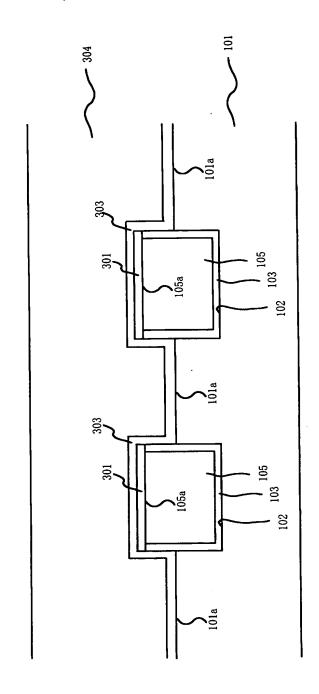

### [0060]

## (4) 第4 実施形態

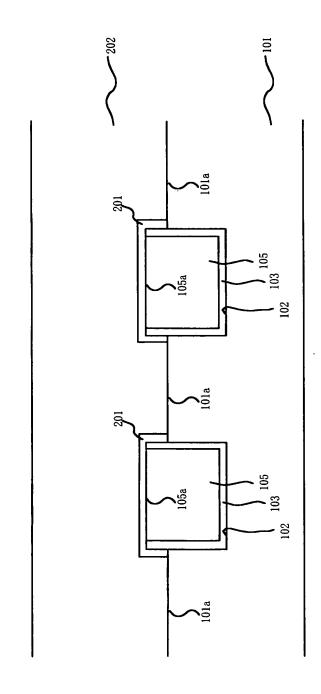

本実施形態に係る半導体装置の配線構造でも、第3実施形態と同様に、配線材料の拡散を防止することにより配線の絶縁耐性を向上させるとともに、配線膜の抵抗のばらつきを抑制することを目的とする。

### [0061]

第3実施形態では、図16の工程においてキャップ膜303をエッチングして溝部10 2ごとに分離したが、キャップ膜303のエッチングを省略しても良い。即ち、図15の 工程の後、図18に示すように、CVD法により、キャップ膜303及び絶縁膜101上に酸化シリコンSiО2 からなる膜厚700nmの絶縁膜304を堆積しても良い。

## [0062]

この場合にも、配線材料Cuのリーク源となる配線膜105の上面105aの縁部と、配線材料によるリーク電流のパスとなる界面101aとが上下方向に離れているので、配線材料Cuが配線膜105からリークしたとしても、リーク電流のパスとなる界面101aに到達し難く、配線材料Cuの拡散を抑制し、配線の絶縁耐性を向上させることができる。

## [0063]

また、配線膜105がキャップ膜301で覆われた状態で絶縁膜101の薄膜化するため、絶縁膜101の薄膜化において、CMP法による研磨によって配線膜105が研磨されて配線膜105の体積が減少することを防止できる。この結果、配線膜105の抵抗のばらつきを抑制できる。また、絶縁膜101をHF処理により薄膜化する場合には、バリア膜103として一般的に使用されるTaからなる膜がエッチングされる懸念があるが、本実施形態のように配線膜105及びバリア膜103をキャップ膜301で覆った状態でエッチングする場合には、Taからなる膜がエッチングされる懸念がない。

### [0064]

また、上記では、キャップ膜301を配線膜105及びバリア膜103よりも広く形成したが、絶縁膜101の薄膜化の際にバリア膜103がエッチングされる虞がない場合には、図22に示すように、配線膜105及びバリア膜103の上面のみにキャップ膜301が残るようにしても良い。配線膜105及びバリア膜103の上面のみにキャップ膜301を形成すれば、隣接するキャップ膜301間の距離、即ち実質的な配線間距離が増大することにより絶縁耐性をさらに向上させることができる。また、キャップ膜301の位置合わせがずれてバリア膜103の上面の一部がキャップ膜301で覆われない場合もあるが、さらにキャップ膜303で覆うため配線膜105が酸化される懸念はない。

### 【図面の簡単な説明】

### [0065]

- 【図1】第1実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図2】第1実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図3】第1実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図4】第1実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図 5 】 第 1 実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図6】第1実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図7】第1実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図8】第1実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図9】第1実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図10】第1実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図11】第2実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図12】第2実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図13】第3実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図14】第3実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図15】第3実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図16】第3実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図17】第3実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図18】第4実施形態に係る半導体装置の配線構造の製造方法を説明する断面図。

- 【図19】ディッシングがある場合の第1実施形態に係る半導体装置の配線構造を説 明する断面図。

- 【図20】キャップ膜106が配線膜105及びバリア膜103の上面のみに形成された場合の第1実施形態に係る半導体装置の配線構造を説明する断面図。

- 【図21】キャップ膜301が配線膜105及びバリア膜103の上面のみに形成さ

れた場合の第3実施形態に係る半導体装置の配線構造を説明する断面図。

【図22】キャップ膜301が配線膜105及びバリア膜103の上面のみに形成された場合の第4実施形態に係る半導体装置の配線構造を説明する断面図。

## 【符号の説明】

[0066]

- 101 第1の絶縁膜

- 101a 第1の絶縁膜の界面

- 102 溝部

- 103 バリア膜

- 104 С u シード膜

- 105 配線膜

- 105a 配線膜の上面

- 106、201、301、303 キャップ膜

- 107、202、304 第2の絶縁膜

- 3 0 2 突起部

【書類名】図面【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

1/E

【書類名】要約書

【要約】。

【課題】 半導体装置の配線構造において、配線材料の拡散を防止することにより配線の 絶縁耐性を向上させるとともに、配線間容量を低減することにある。

【解決手段】 複数の溝部102が形成されており、隣接する溝部102の間に水平方向の界面101aを有する第1絶縁膜101と、第1絶縁膜101の溝部102ごとに界面102aよりも突出して形成された複数の配線膜105と、配線膜105の底面に形成されるとともに、配線膜105の側面において界面101aより上方まで形成されている複数のバリア膜103と、少なくとも配線膜105の上面に形成されており、溝部102ごとに分離されている複数のキャップ膜106と、を備えることを特徴とする半導体装置の配線構造。

【選択図】 図10

# 特願2003-367951

# 出願人履歴情報

識別番号

[000000295]

1. 変更年月日

1990年 8月22日

[変更理由]

新規登録

住 所

東京都港区虎ノ門1丁目7番12号

氏 名 沖電気工業株式会社